CS47L35 是 Cirrus Logic 推出的一款高性能、低功耗音频编解码器(Audio Codec),专为智能手机、可穿戴设备、蓝牙耳机、智能音箱等音频设备设计。它集成了高品质的 DAC(数字-模拟转换)、ADC(模拟-数字转换)、低功耗 DSP(数字信号处理器)和语音增强功能,支持多种音频输入/输出接口,能够实现高质量音频播放、录音、降噪和回声消除等功能。

电气特性

模拟电源(AVDD):1.7V ~ 1.9V

数字核心电源(DBVDD):1.2V

I/O 电源(IOVDD):1.8V 或 3.3V

耳机驱动电源(HPVDD):2.5V ~ 5V(典型 3.3V)

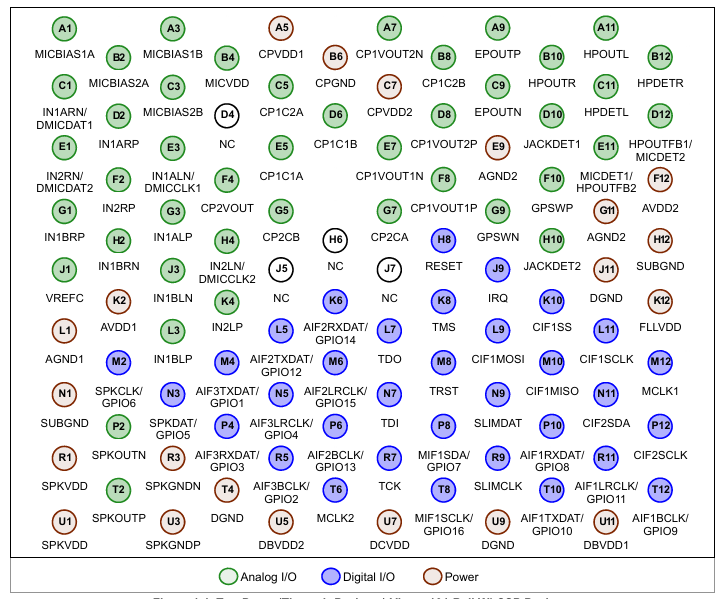

引脚说明

| 引脚名称 | 引脚编号 | 功率供应 | I/O 类型 | 功能描述 |

|---|---|---|---|---|

| CP1C1A | E5 | O | Analog I/O | 电荷泵 1 正向电容引脚 1。 |

| CP1C1B | D6 | O | Analog I/O | 电荷泵 1 正向电容引脚 2 |

| CP1C2A | C5 | O | Analog I/O | 电荷泵 1 反向电容引脚 1。 |

| CP1C2B | B8 | O | Analog I/O | 电荷泵 1 反向电容引脚 2。 |

| CP1VOUT1P | E7 | O | Analog I/O | 电荷泵 1 输出正电压。 |

| CP1VOUT1N | F8 | O | Analog I/O | 电荷泵 1 输出负电压。 |

| CP1VOUT2P | A7 | O | Analog I/O | 电荷泵 1 正向电压输出 2。 |

| CP1VOUT2N | D8 | O | Analog I/O | 电荷泵 1 反向电压输出 2。 |

| CP2CA | G7 | O | Analog I/O | 电荷泵 2 正向电容引脚。 |

| CP2CB | G5 | O | Analog I/O | 电荷泵 2 反向电容引脚。 |

| CP2VOUT | F4 | O | Analog I/O | 电荷泵 2 输出电压供电/解耦。 |

| EPOUTN | C9 | O | Analog I/O | 耳机输出负电压。 |

| EPOUTP | A9 | O | Analog I/O | 耳机输出正电压。 |

| GPSWN | G9 | I/O | General I/O | 通用双向开关引脚。 |

| GPSWP | F10 | I/O | General I/O | 通用双向开关引脚。 |

| HPDET | C11 | I | Analog I/O | 耳机输入检测。 |

| HPOUTL | B12 | I | Analog I/O | 左耳机输出输入。 |

| HPOUTR | A11 | I | Analog I/O | 右耳机输出输入。 |

| HPOUT | D12 | I | Analog I/O | 耳机输出反馈引脚,连接外部麦克风及耳机输入。 |

| IN1ALP | E3 | I | Analog I/O | 左通道单端输入/左通道正向输入信号。 |

| IN1ALP | G3 | I | Analog I/O | 左通道单端输入/左通道正向输入信号。 |

| IN1BRP | H2 | I | Analog I/O | 右通道单端输入/右通道正向输入信号。 |

| IN2BLP | H4 | I | Analog I/O | 左通道负向输入信号。 |

| IN2BRP | H6 | I | Analog I/O | 右通道负向输入信号。 |

| IN2ALP | K6 | I | Analog I/O | 左通道负向输入信号。 |

| IN2BRP | K7 | I | Analog I/O | 右通道负向输入信号。 |

| IN2LP | K4 | MICVDD | I | 左通道单端麦克风输入/左通道正向差分输入信号。 |

| IN2RN/DMICDAT2 | E1 | MICVDD 或 MICBIASn | I | 右通道单端麦克风输入/右通道正向差分输入信号。 |

| IN2RP | F2 | MICVDD | I | 右通道单端麦克风输入/右通道正向差分输入信号。 |

| JACKDET1 | D10 | AVDD | I | 插孔检测输入 1。 |

| JACKDET2 | H10 | AVDD | I | 插孔检测输入 2。 |

| MICBISA1 | A1 | O | Analog I/O | 麦克风偏置 1A。 |

| MICBISA1B | A3 | O | Analog I/O | 麦克风偏置 1B。 |

| MICBISA2 | B2 | O | Analog I/O | 麦克风偏置 2A。 |

| MICBISA2B | C3 | O | Analog I/O | 麦克风偏置 2B。 |

| MICDET1/HPOUTFB2 | E11 | I | Analog I/O | 麦克风和配件传感器输入,连接到 1/HPOUTL 和 HPOUTR 地线反馈。 |

| MICVDD | B4 | O | Analog I/O | LDO 输出解耦引脚(由 CS47L35 内部生成)。可用于外部麦克风的参考/供电。 |

| SPKOUT | P2 | O | Analog I/O | 扬声器负输出。 |

| SPKOUT | T2 | O | Analog I/O | 扬声器正输出。 |

| VREFC | J1 | I | Analog I/O | 带隙参考电容连接。 |

| AIF1BCLK/GPIO | T12 | DBVDD1 | I/O | 音频接口 1 帧时钟/GPIO。GPIO 输出可以选择 CMOS 或开漏;BCLK 输出为 CMOS。 |

| AIF1LRCLK/GPIO | R11 | DBVDD1 | I/O | 音频接口 1 左右时钟/GPIO。GPIO 输出可以选择 CMOS 或开漏;LRCLK 输出为 CMOS。 |

| AIF1RXDAT/GPIO | P10 | DBVDD1 | I/O | 音频接口 1 RX 数字音频数据/GPIO。GPIO 输出可以选择 CMOS 或开漏;TXDAT 输出为 CMOS。 |

| AIF1TXDAT/GPIO | T10 | DBVDD1 | I/O | 音频接口 1 TX 数字音频数据/GPIO。GPIO 输出可以选择 CMOS 或开漏;TXDAT 输出为 CMOS。 |

| AIF2BCLK/GPIO | P6 | DBVDD2 | I/O | 音频接口 2 帧时钟/GPIO。GPIO 输出可以选择 CMOS 或开漏;BCLK 输出为 CMOS。 |

| AIF2LRCLK/GPIO | M6 | DBVDD2 | I/O | 音频接口 2 左右时钟/GPIO。GPIO 输出可以选择 CMOS 或开漏;LRCLK 输出为 CMOS。 |

| AIF2RXDAT/GPIO | P8 | DBVDD2 | I/O | 音频接口 2 RX 数字音频数据/GPIO。GPIO 输出可以选择 CMOS 或开漏;TXDAT 输出为 CMOS。 |

| AIF2TXDAT/GPIO | M10 | DBVDD2 | I/O | 音频接口 2 TX 数字音频数据/GPIO。GPIO 输出可以选择 CMOS 或开漏;TXDAT 输出为 CMOS。 |

| AIF3BCLK/GPIO | R5 | DBVDD2 | I/O | 音频接口 3 帧时钟/GPIO。GPIO 输出可以选择 CMOS 或开漏;BCLK 输出为 CMOS。 |

| AIF3RXDAT/GPIO | N5 | DBVDD2 | I/O | 音频接口 3 RX 数字音频数据/GPIO。GPIO 输出可以选择 CMOS 或开漏;TXDAT 输出为 CMOS。 |

| CIF1MSIO | M10 | DBVDD1 | I/O | 控制接口 1 SPI 主模式与从模式。CIF1S 时钟在未选择时为高阻态。 |

| CIF1SCLK | L9 | DBVDD1 | I/O | 控制接口 1 SPI 时钟。CIF1S 时钟在未选择时为高阻态。 |

| CIF1CSLCK | K7 | DBVDD1 | I/O | 控制接口 1 SPI 片选信号。 |

| CIF2SDA | N11 | DBVDD1 | I/O | 控制接口 2 (I²C) 数据输入输出。SDA 输出为开漏。 |

| IRQ | J9 | DBVDD1 | I | 中断请求输出(低电平有效)。引脚配置可选择 CMOS 或开漏。 |

| MCLK1 | M12 | DBVDD1 | I | 主时钟输入 1。 |

| MCLK2 | T6 | DBVDD2 | I | 主时钟输入 2。 |

| MIF1SCLK/GPIO | T8 | DBVDD1 | I/O | 控制接口 1 时钟输出/GPIO。GPIO 输出可选择 CMOS 或开漏;SCLK 输出为 CMOS。 |

| MIF1SDA/GPIO | P6 | DBVDD1 | I/O | 控制接口 1 数据输入/GPIO。GPIO 输出可选择 CMOS 或开漏;SDA 输出为开漏。 |

| RESET | H8 | DBVDD1 | I | 数字复位输入(激活有效)。 |

| SLIMCLK | R9 | DBVDD1 | I/O | SLIMbus 时钟输入输出。 |

| SLIMDAT | N9 | DBVDD1 | I/O | SLIMbus 数据输入输出。 |

| SPKDAT/GPIO | N3 | DBVDD2 | I/O | 数字扬声器 (PDM) 数据输出/GPIO。GPIO 输出可选择 CMOS 或开漏;SPKDAT 输出为 CMOS。 |

| TCK | R7 | DBVDD2 | I | JTAG 时钟输入。内部下拉保持此引脚为逻辑 0,正常工作时有效。 |

| TDI | N7 | DBVDD2 | I | JTAG 数据输入。内部下拉保持此引脚为逻辑 0,正常工作时有效。 |

| TDO | L7 | DBVDD2 | O | JTAG 数据输出。 |

| TMS | K8 | DBVDD2 | I | JTAG 模式选择输入。内部下拉保持此引脚为逻辑 0,正常工作时有效。 |

| TRST | M8 | DBVDD2 | I | JTAG 复位输入(激活有效)。内部下拉保持此引脚为逻辑 0,正常工作时有效。 |

| AGND1 | L1 | — | I | 模拟接地(返回 AVDD1)。 |

| AGND2 | E9 | — | I | 模拟接地(返回 AVDD2)。 |

| AVDD1 | K2 | — | O | 模拟电源 1。 |

| AVDD2 | F12 | — | O | 模拟电源 2。 |

| CPVDD | D6 | — | O | 电荷泵电源,供给电荷泵 1 和电荷泵 2。 |

| DBVDD1 | U11 | — | O | 数字电源(供音频接口、SLIMbus、控制接口等使用)。 |

| DBVDD2 | U5 | — | O | 数字电源(供音频接口、SLIMbus、控制接口等使用)。 |

| DCVDD | U7 | — | — | 数字核心电源供应。 |

| DGND | J11, T4, U9 | — | — | 数字地(DCVDD 和 DBVDDn 的返回路径)。 |

| FLLVDD | K12 | — | — | 模拟电源(用于 FLL1)。 |

| SPKGNDN | R3 | — | — | 扬声器驱动地(SPKVDD 的返回路径)。¹ |

| SPKGNDP | U3 | — | — | 扬声器驱动地(SPKVDD 的返回路径)。¹ |

| SPKVDD | R1, U1 | — | — | 扬声器驱动电源供应。 |

| SUBGND | H12, N1 | — | — | 基板地(Substrate ground)。 |

| NC | D4, H6, J5, J7 |

本芯片 CS47L35 具有丰富的 音频输入/输出接口、GPIO、I²C/SPI 控制接口 以及 JTAG 调试接口,并配备多种 电源管理和地连接。主要特点:

- 支持模拟和数字麦克风输入

- 具备 3 组 I²S 接口,可用于音频数据传输

- 内置 PDM 扬声器接口

- 提供 SPI 和 I²C 作为控制接口

- 具备 JTAG 调试支持

- 内置充电泵、多个电源域,提高功耗管理

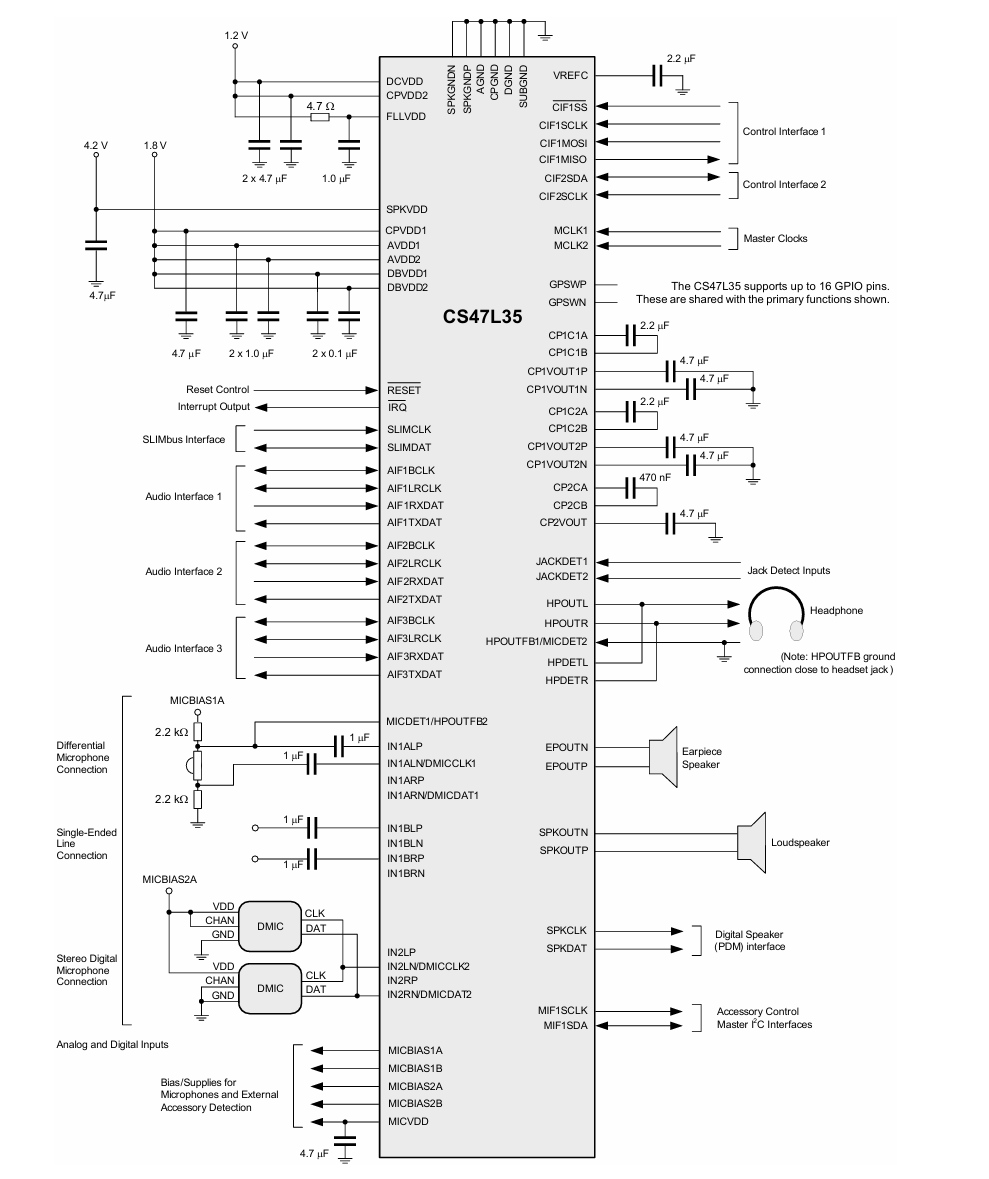

应用电路

典型应用电路

DVDD、DBVDD、FLVDD(1.2V):芯片的 数字核心供电,通常由 LDO 或 DCDC 提供。

AVDD(1.8V):模拟电路供电,驱动麦克风偏置和 ADC。

CPVDD(2.5V~4V):内部 电荷泵供电,用于耳机放大。

SPKVDD(3.3V~5V):提供扬声器输出的电源。

电源去耦电容(如 4.7µF、1µF):用于降低电源噪声。

RESET:复位引脚,通常连接到 MCU 以进行芯片复位。

IRQ:中断信号输出,可通知 MCU 处理特定事件。

SLIMBus / I²S(AIFxBCLK、AIFxLRCLK、AIFxRXDAT、AIFxTXDAT)

- 该芯片支持 SLIMBus 和 I²S/TDM 接口,用于音频数据传输。

- I²S 用于与 MCU 或 DSP 通信,传输麦克风和扬声器数据。

麦克风输入(MICBIAS、IN1A/IN1B、IN2A/IN2B)

- 支持 差分麦克风 和 单端麦克风。

- MICBIAS 提供偏置电压(2.2kΩ 上拉到 MICBIAS)。

- 可以连接到 数字 MEMS 麦克风(PDM) 通过 I²S/TDM 接收音频数据。

耳机输出(HPOUTL、HPOUTR)

- 连接到 3.5mm 耳机插孔,支持 立体声耳机。

- HPDETR(耳机检测引脚)用于检测是否插入耳机。

- EPOUTP/EPOUTN:支持 BTL(桥接负载)耳机驱动,提供更高功率输出。

扬声器输出(SPKOUTP、SPKOUTN)

- 连接到 扬声器,支持单声道 BTL(桥接负载)驱动。

- SPKVDD 提供功率,支持更大功率输出。

数字扬声器输出(SPKDAT)

- 通过数字 I²S/TDM 发送音频信号到外部 D 类放大器。

GPIOS

- 支持 多达 16 个 GPIO,用于控制音频路径、检测插拔、调节增益等。

MCLK(时钟输入)

- 提供芯片运行所需的 主时钟(MCLK1/MCLK2)。

工作原理

音频信号处理流程

音频输入:

- 模拟音频信号(如麦克风输入)通过 ADC(模数转换器)转换为数字信号。

- 数字音频信号可通过 I²S 或 PDM 接口直接输入芯片。

音频信号处理(DSP):

- 语音增强(Beamforming、降噪、回声消除等)。

- 音效处理(如均衡器、混响等)。

音频输出:

- 处理后的音频信号可通过 DAC(数模转换器)转换为模拟信号,并通过耳机放大器驱动耳机或扬声器。

- 也可以以数字信号的形式通过 I²S 或 TDM 发送到外部设备。

通信方式

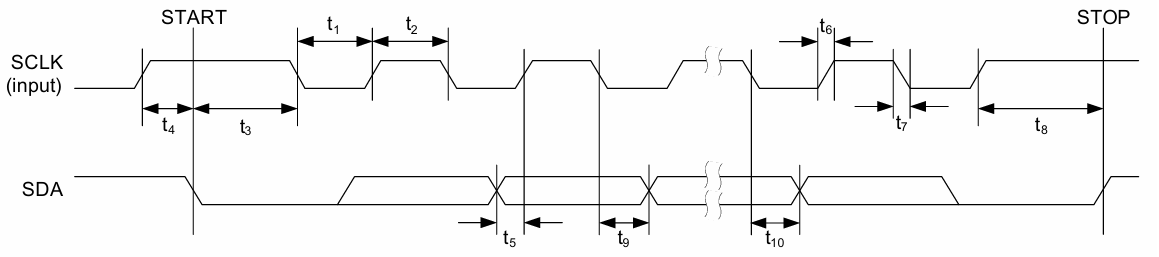

I2C通信

I2C(Two-Wire)模式下控制接口的时序要求

| 参数 | 符号 | 最小值(Min) | 典型值(Typ) | 最大值(Max) | 单位 |

|---|---|---|---|---|---|

| SCL 时钟频率 | f_SCL | — | — | 3400 | kHz |

| SCL 低脉冲宽度 | t1 | 160 | — | — | ns |

| SCL 高脉冲宽度 | t2 | 160 | — | — | ns |

| 启动条件保持时间 | t3 | 160 | — | — | ns |

| 启动条件设置时间 | t4 | 160 | — | — | ns |

| SDA, SCL 上升时间(10%-90%) | t5 | SCL 频率 > 1.7MHz | — | 80 | ns |

| SDA, SCL 上升时间(10%-90%) | t5 | SCL 频率 ≤ 1MHz | — | 2000 | ns |

| SDA, SCL 降落时间(90%-10%) | t6 | SCL 频率 > 1.7MHz | — | 160 | ns |

| SDA, SCL 降落时间(90%-10%) | t6 | SCL 频率 ≤ 1MHz | — | 200 | ns |

| 停止条件设置时间 | t7 | 160 | — | — | ns |

| SDA 设置时间(数据输入) | t8 | 40 | — | — | ns |

| SDA 保持时间(数据输入/ACK 输出) | t9 | 0 | — | 40 | ns |

| SDA 保持时间(数据输入) | t10 | SCL 上升时间(90%-10%)= 20ns, C_LOAD(SDA)= 15pF | — | 40 | ns |

| SDA 保持时间(数据输入) | t10 | SCL 上升时间(90%-10%)= 60ns, C_LOAD(SDA)= 100pF | — | 130 | ns |

| SDA 保持时间(数据输入) | t10 | SCL 上升时间(90%-10%)= 160ns, C_LOAD(SDA)= 400pF | — | 190 | ns |

| SDA 保持时间(数据输入) | t10 | SCL 上升时间(90%-10%)= 200ns, C_LOAD(SDA)= 550pF | — | 220 | ns |

| 时序波形脉冲 | tps | 0 | — | 25 | ns |

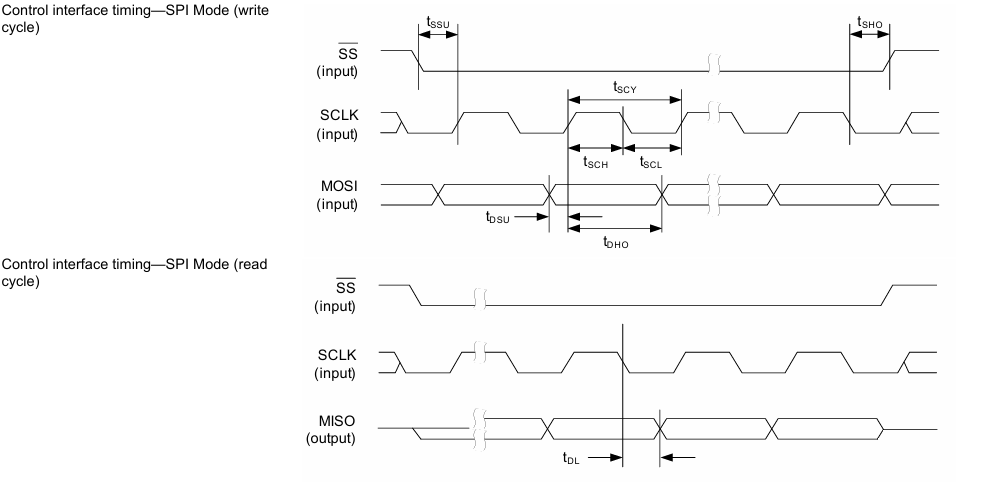

SPI通信

SPI(Serial Peripheral Interface)四线模式 的控制接口时序要求

| 参数 | 符号 | 最小值(Min) | 典型值(Typ) | 最大值(Max) | 单位 |

|---|---|---|---|---|---|

| SS 到 SCLK 上升沿的时间 | t_ssu | 2.6 | — | — | ns |

| SCLK 到 SS 上升沿的时间 | t_sho | 0 | — | — | ns |

| SCLK 脉冲周期时间 | t_scy | 50.0 | — | — | ns |

| SCLK 脉冲周期时间(系统时钟禁用时) | t_scy | 76.8 | — | — | ns |

| SCLK 脉冲周期时间(SYSCLK 频率 > 000 时) | t_scy | 38.4 | — | — | ns |

| SCLK 低电平宽度 | t_scl | 15.3 | — | — | ns |

| SCLK 高电平宽度 | t_sch | 15.3 | — | — | ns |

| MOSI 到 SCLK 设置时间 | t_msu | 1.5 | — | — | ns |

| MOSI 到 SCLK 保持时间 | t_mho | 1.7 | — | — | ns |

| SCLK 上升沿到 MISO 传输的时间 | t_su | 0 | — | 12.6 | ns |